FAKULTÄT FÜR !NFORMATIK

**Faculty of Informatics**

# Virtual HW/SW Prototyping for Design and Runtime Prediction of Parallel Video Coding Systems

## DISSERTATION

zur Erlangung des akademischen Grades

## Doktor der technischen Wissenschaften

eingereicht von

### **Florian Seitner**

Matrikelnummer 9925654

an der Fakultät für Informatik der Technischen Universität Wien

Betreuung: ao. Univ.-Prof. Mag. Dipl.-Ing. Dr.techn. Margrit Gelautz

Diese Dissertation haben begutachtet:

(ao. Univ.-Prof. Mag. Dipl.-Ing. Dr.techn. Margrit Gelautz) (Univ.-Prof. Dipl.-Ing. Dr.techn. Bernhard Rinner)

Wien, 11. Oktober 2013

(Florian Seitner)

## Erklärung zur Verfassung der Arbeit

Florian Seitner Hietzinger Hauptstraße 56/1/8, 1130 Wien

Hiermit erkläre ich, dass ich diese Arbeit selbständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit einschließlich Tabellen, Karten und Abbildungen -, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind, auf jeden Fall unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

(Ort, Datum)

(Unterschrift Verfasser)

## Acknowledgements

First of all, I want to thank my supervisor Margrit Gelautz for her constant support and encouragement throughout the years that I spent as a PhD student. She forged my skills in research and scientific writing and without her guidance, this work would not have been possible. I am grateful to Bernhard Rinner who kindly agreed to be the second reviewer of this thesis.

During my studies, I also had the pleasure to work with Michael Bleyer. His feedback and countless hours of joint work before various submission deadlines proved to be of enormous value for my research. I would like to thank Ralf Beuschel for introducing me to the field of video coding and showing me the importance of structured scientific working in an industrial environment. I would also like to acknowledge Tom Wilson for proofreading this thesis and for supporting me in finding time to finish this thesis.

Many thanks go to all of my colleagues in the Interactive Media Systems Group and at OnDemand Microelectronics who offered me the opportunity for many interesting discussions and a nice and productive working atmosphere.

I would like to thank the Austrian Federal Ministry of Transport, Innovation, and Technology (BMVIT) for its financial support of this thesis under the FIT-IT project VENDOR (Project no. 812429).

I would further like to express my thankfulness to my friends. (I do not put any names, since I am afraid to forget someone.) Their support and the ability to enjoy my life outside the pages of my thesis were always a great source of inspiration. I would also like to thank my family, especially my mother and father, who made it possible for me to study.

Finally, special thanks go to my beloved wife Julia for her support and patience during all these years. A thesis is like a marathon and she gave me support from the first to the last kilometer.

## Abstract

The high computational demands of state-of-the-art video coding standards such as H.264 pose serious challenges on embedded processor architectures. A natural way to tackle this problem is the use of multi-processor systems. However, the efficient distribution of complex video coding algorithms among multiple processing units (PUs) is a non-trivial task. In order to use the available processing resources efficiently, an equally balanced distribution of the coding algorithm onto the hardware units must be found. The system designer has to consider data-dependency issues as well as inter-communication and synchronization between the PUs. Furthermore, efficient software design is necessary in order to satisfy the resource limitations in an embedded environment, such as low computational power, small-sized on-chip memories and low bus bandwidth. A parallel video coding implementation for an embedded system must be able to work under these resource restrictions.

Being able to predict the resource requirements of a parallel video coding application (VCA) is therefore essential during the design of a video coding system (VCS) considering these strict requirements on runtime performance and resource usage. This thesis contributes novel methods to support the complex design process of parallel VCS in an early phase of system design when highly critical decisions on hardware and software are made. The contributions of this thesis can be summarised as follows. (i) We propose the *Data-Driven Profiling* (DDP) method for analysing and visualizing the runtime complexity of a VCS. This method maps traditional runtime profilings onto the coding elements and functional blocks of a video coding algorithm. It enables the system designer to relate runtime complexity with the application levels where parallelisation takes place and introduces means for analysing the workload distribution. (ii) We demonstrate how to exploit DDPs for analysing complexity and deriving essential information for parallel system design. Assumptions about the performance of a VCA on a parallel architecture can be made, potential problems in work balancing identified and complexity variations in the functional blocks of a VCA's video coding elements analysed. (iii) We introduce the Partition Assessment Simulation (PAS) methodology for enabling the exploration of complex parallel VCS designs. This methodology exploits the structural and functional similarities of modern video coding algorithms for predicting a VCA's runtime on a "virtual" architecture. (iv) We implement a simulator for the PAS concept. By modelling and simulating an existing multi-processor platform, the PAS methodology is verified. We demonstrate the flexibility of the PAS to simulate complex parallel video coding platforms and to explore new parallel designs for functional as well as data-parallel H.264 decoder partitioning methods. We believe that the contributed techniques enable system designers to address the challenges of parallel VCS design in an intuitive and time-efficient way leading to application-tailored and cost-competitive VCS.

## Kurzfassung

Die hohen Anforderungen, die moderne Videokodierstandards an die Rechenleistung stellen, können auf vielen Embedded-Architekturen nicht oder nur eingeschränkt gelöst werden. Der Einsatz von Multi-Prozessorsystemen und die Aufteilung der Kodierung auf mehrere Prozessoren bieten hier eine elegante Lösung. Der Entwurf von parallelen Videokodiersystemen stellt jedoch bei komplexen Algorithmen wie H.264 eine herausfordernde Aufgabe dar. Es gilt hier, eine gleichmäßige Aufteilung der Rechenschritte auf die verfügbaren Prozessoren zu finden und dabei bei der Partitionierung die hohe Anzahl an algorithmischen Abhängigkeiten zwischen den einzelnen Schritten zu berücksichtigen. Des Weiteren müssen architekturbedingte Ressourcenlimits wie z. B. die Speichergröße berücksichtigt werden.

Diese Arbeit widmet sich der Performanceanalyse und -vorhersage von parallelen Videokodiersystemen. Der wissenschaftliche Beitrag dieser Arbeit umfasst zwei Methoden, um die Laufzeit von Videokodieralgorithmen effizient zu analysieren und bereits in früheren Phasen des Designprozesses Annahmen über die Eigenschaft des Gesamtsystems treffen zu können. Die erste Methode, das Data-Driven Profiling (DDP), ermöglicht es, die Laufzeit eines Videokodiersystems im Zusammenhang mit den zu verarbeitenden Daten zu analysieren. Dabei werden traditionelle Laufzeitprofile automatisch auf die Kodierelemente und -schritte des Kodieralgorithmus abgebildet. DDP gibt Aufschluss über die Laufzeit, die für die Kodierung einzelner Kodierelemente und funktionaler Kodierblöcke aufgewendet wird und wie diese das Laufzeitverhalten von parallelen Videokodiersystemen beeinflussen. Die zweite Methode, die Partition Assessment Simulation (PAS), macht sich strukturelle und funktionale Charakteristika hybrider Videokodieralgorithmen zunutze, um Laufzeitabschätzungen für virtuelle Architekturen zur Videokodierung zu treffen. Diese Methode baut auf DDP sowie Konzepten der simulationsbasierten Laufzeitvorhersage auf und ermöglicht bereits in einer frühen Phase der Systementwicklung das Ausprobieren unterschiedlicher Designvarianten und das schnelle Adaptieren von parallelen Videokodiersystemen an Designvorgaben. Diese Arbeit beschreibt eine konkrete Implementierung für das PAS Konzept und liefert mit Hilfe einer bestehenden Multiprozessorarchitektur eine Verifikation und Genauigkeitsanalyse. Die Flexibilität, neue Designmöglichkeiten zu erschließen, wird anhand konkreter Beispiele demonstriert.

Die vorgestellten Techniken ermöglichen es, beim Design von parallelen Videokodiersystemen gezielt und anwendungsspezifisch auf Komplexität und benötigte Hardwareresourcen einzugehen. Bereits in einer frühen Phase des Designprozesses können Abschätzungen über das Laufzeitverhalten des Designs gemacht und dadurch das Entwicklungsrisiko signifikant gesenkt werden.

## Contents

| Li | st of I | Figures                                                  | xiii  |

|----|---------|----------------------------------------------------------|-------|

| Li | st of T | Fables                                                   | xv    |

| Li | st of A | Abbreviations                                            | xviii |

| 1  | Intro   | oduction                                                 | 1     |

|    | 1.1     | Design of parallel video coding architectures            | 1     |

|    | 1.2     | Motivation and objectives                                | 2     |

|    | 1.3     | Contributions                                            | 3     |

|    | 1.4     | Resulting publications                                   | 4     |

|    | 1.5     | Organization                                             | 5     |

| 2  | Prio    | or work on complexity and runtime estimation             | 7     |

|    | 2.1     | Analytic runtime prediction                              | 7     |

|    | 2.2     | Runtime prediction based on dynamic profiling            | 8     |

|    |         | 2.2.1 Statistical profiling                              | 10    |

|    |         | 2.2.2 Instrumented profiling                             | 10    |

|    | 2.3     | Simulation-based runtime prediction                      | 13    |

|    |         | 2.3.1 Hardware simulation techniques                     | 13    |

|    |         | 2.3.2 Instruction set simulation                         | 13    |

|    |         | 2.3.3 HW/SW-codesign                                     | 14    |

|    | 2.4     | High-level design exploration                            | 15    |

|    | 2.5     | Partition Assessment Simulation in context of prior work | 15    |

|    | 2.6     | Summary                                                  | 16    |

| 3  | Cha     | racteristics of modern video coding algorithms           | 17    |

|    | 3.1     | Historical development of digital video coding           | 17    |

|    | 3.2     | Concept of hybrid video coding                           | 19    |

|    | 3.3     | Hierarchical structuring of video coding elements        | 21    |

|    | 3.4     | Coding tools                                             | 22    |

|    |         | 3.4.1 Spatial prediction                                 | 22    |

|    |         | 3.4.2 Motion-compensated prediction                      | 23    |

|    |         | 3.4.3 Transformation and quantisation of residual data   | 27    |

|   |                    | 3.4.4    | Deblocking filter                                            | 27       |

|---|--------------------|----------|--------------------------------------------------------------|----------|

|   |                    | 3.4.5    | Entropy coding                                               | 28       |

|   | 3.5                | Paralle  | l video decoding                                             | 28       |

|   |                    | 3.5.1    | Dependencies between macroblocks                             | 29       |

|   |                    | 3.5.2    | Functional partitioning                                      | 30       |

|   |                    | 3.5.3    | Data-parallel partitioning                                   | 31       |

|   | 3.6                |          | ary                                                          | 36       |

| 4 | Data               | duiron   | muntime analyzia                                             | 39       |

| 4 | <b>Data</b><br>4.1 |          | runtime analysis                                             | 39<br>39 |

|   | 4.1                |          | atic generation of data-driven profiles                      | 41       |

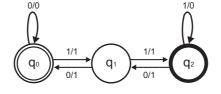

|   | 4.2                | 4.2.1    | Finite State Machines and Pushdown Automatons                | 41       |

|   |                    | 4.2.1    |                                                              | 42       |

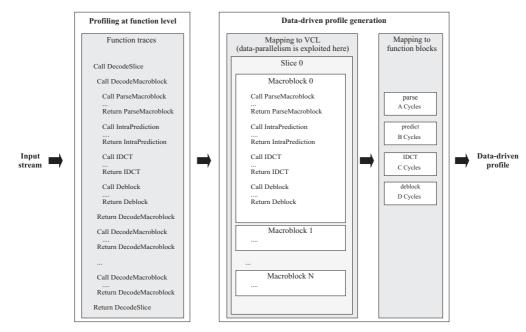

|   |                    |          | Mapping profiling information to VCL and functional blocks   | 45<br>45 |

|   |                    | 4.2.3    | Extraction of coding information via function names          | 45<br>46 |

|   |                    | 4.2.4    | Extraction of coding information via instrumentation         |          |

|   | 1.2                | 4.2.5    | Implementation                                               | 46       |

|   | 4.3                |          | Before and test sequences                                    | 47       |

|   |                    | 4.3.1    | Reference architecture                                       | 47       |

|   | 4 4                | 4.3.2    | Test sequences                                               | 50       |

|   | 4.4                | -        | mental results for runtime analysis and visualization        | 55       |

|   |                    | 4.4.1    | Complexity of processing VCL coding elements                 | 55       |

|   |                    | 4.4.2    | Complexity of processing functional blocks                   | 58       |

|   |                    | 4.4.3    | Analysing complexity within individual subregions of a frame | 60       |

|   | 4.5                | Summa    | ary                                                          | 62       |

| 5 | Virt               | -        | otyping of parallel video coding systems                     | 63       |

|   | 5.1                |          | l aspects and design goals                                   | 63       |

|   | 5.2                | Concep   | pt                                                           | 64       |

|   |                    | 5.2.1    | System specification                                         | 65       |

|   |                    | 5.2.2    | Characterisation                                             | 72       |

|   |                    | 5.2.3    | Simulation                                                   | 73       |

|   | 5.3                | Implen   | nentation of the Partition Assessment Simulation             | 75       |

|   |                    | 5.3.1    | Time domains within PAS                                      | 75       |

|   |                    | 5.3.2    | Task generation based on data-driven profiling               | 76       |

|   |                    | 5.3.3    | Rule-based specification of data-dependencies                | 76       |

|   |                    | 5.3.4    | Partitioning of video coding application                     | 77       |

|   |                    | 5.3.5    | Simulation process                                           | 78       |

|   | 5.4                | Summa    | ary                                                          | 81       |

| 6 | Con                | cept ver | ification and design space exploration results               | 83       |

| - | 6.1                | -        | cation of a dual-core video coding system                    | 83       |

|   | 6.2                |          | terisation of virtual hardware                               | 84       |

|   | 6.3                |          | ation using a functional dual-core decoder splitting         | 87       |

|   | 6.4                |          | space exploration                                            | 91       |

|   | 0.1                | 2001611  | space experiment                                             | 1        |

| Bi | bliogr | aphy                                                    | 105 |

|----|--------|---------------------------------------------------------|-----|

| A  | Deta   | iled description of test sequences                      | 99  |

|    | 7.2    | Open topics for future research                         | 97  |

|    |        | 7.1.2 Modelling and simulation of virtual architectures | 96  |

|    |        | 7.1.1 Analysis of VCA runtime behaviour                 | 95  |

|    | 7.1    | Conclusions                                             | 95  |

| 7  | Con    | clusions and future work                                | 95  |

|    | 6.5    | Summary                                                 | 94  |

|    |        | 6.4.3 Alternative processor for parsing                 | 94  |

|    |        | 6.4.2 Data-parallel partitioning                        | 93  |

|    |        | 6.4.1 Functional partitioning                           | 91  |

# **List of Figures**

| 2.1  | A simple control flow graph (CFG).                                           | 9  |

|------|------------------------------------------------------------------------------|----|

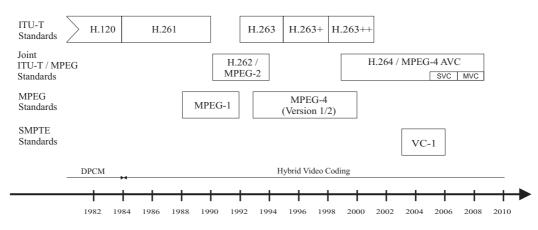

| 3.1  | Historical development of international digital video coding standards       | 18 |

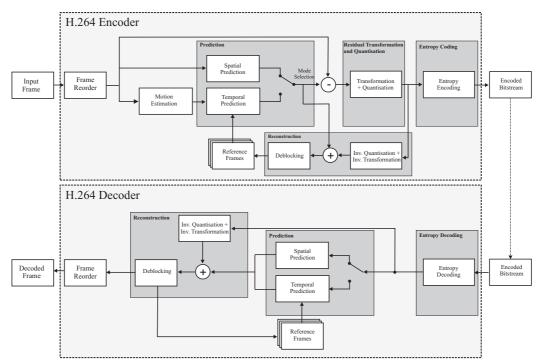

| 3.2  | H.264 encoder and decoder structure.                                         | 20 |

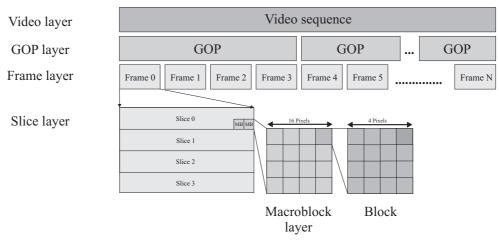

| 3.3  | Hierarchical structuring of a video stream in the H.264 standard.            | 22 |

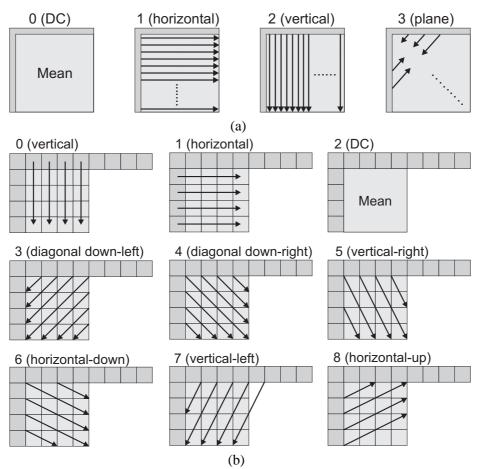

| 3.4  | H.264 intra-prediction modes.                                                | 23 |

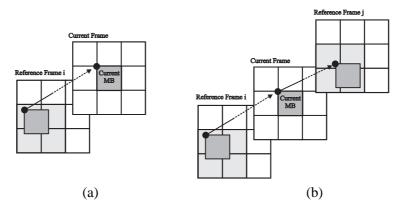

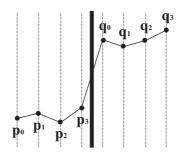

| 3.5  | Temporal prediction of macroblocks between frames.                           | 24 |

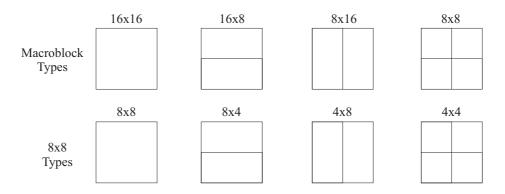

| 3.6  | H.264 inter prediction macroblock partitioning.                              | 24 |

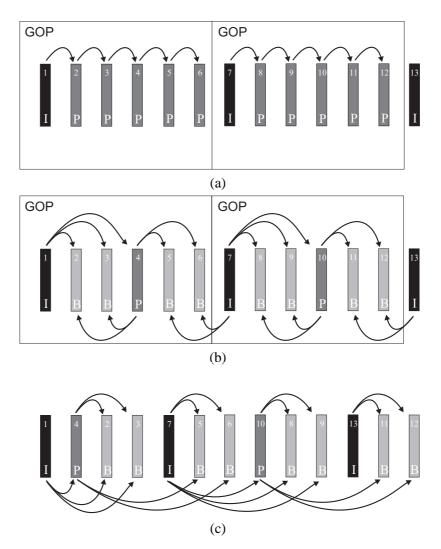

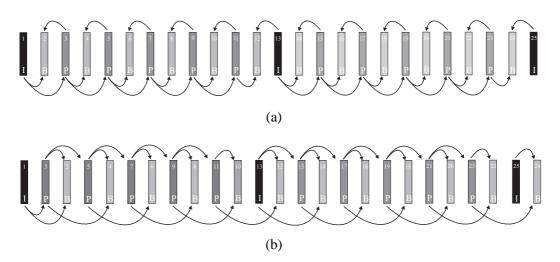

| 3.7  | GOP-Coding.                                                                  | 26 |

| 3.8  | Visualisation of block edge deblocking in H.264.                             | 28 |

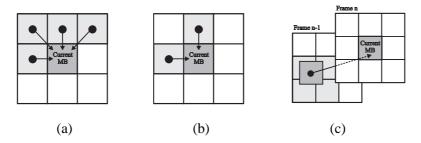

| 3.9  | Macroblock dependencies in H.264 decoding                                    | 29 |

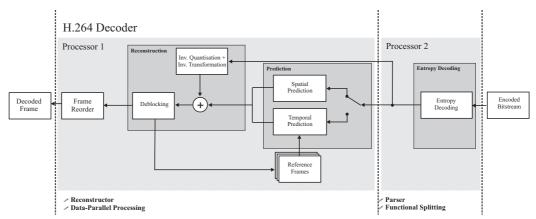

| 3.10 | Functional split of an H.264 decoder.                                        | 30 |

| 3.11 | The Single-row splitting approach.                                           | 31 |

| 3.12 | Example of the Single-row splitting approach used with two cores             | 31 |

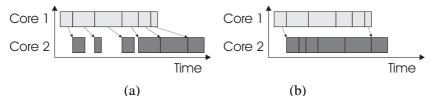

|      | Inter-processor dependencies in a multi-core system                          | 33 |

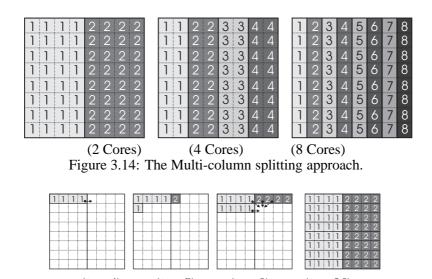

| 3.14 | The Multi-column splitting approach.                                         | 33 |

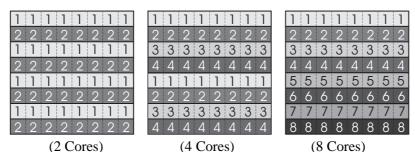

| 3.15 | Example of the Multi-column splitting approach                               | 33 |

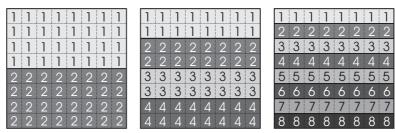

| 3.16 | The Slice-parallel splitting approach                                        | 34 |

| 3.17 | Example of the Slice-parallel splitting approach in the blocking version     | 34 |

| 3.18 | Example of the Slice-parallel splitting approach in the non-blocking version | 34 |

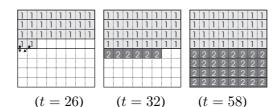

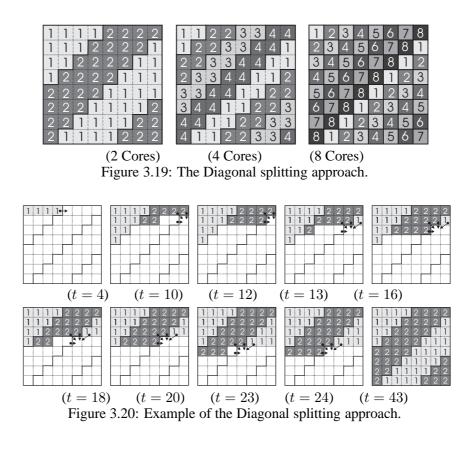

| 3.19 | The Diagonal splitting approach                                              | 36 |

| 3.20 | Example of the Diagonal splitting approach                                   | 36 |

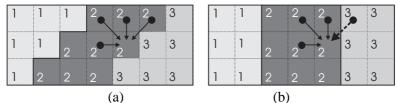

| 3.21 | Dependencies in the Diagonal and Multi-column splitting approaches           | 36 |

| 4.1  | Data-driven profiling at macroblock level                                    | 41 |

| 4.2  | Example of a state transition diagram.                                       | 42 |

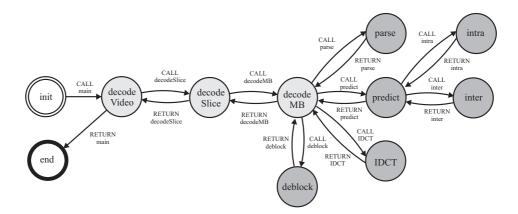

| 4.3  | Example of a state transition diagram for an H.264 decoder                   | 44 |

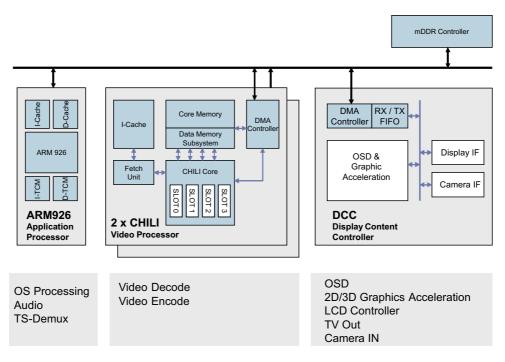

| 4.4  | Structure of the SVENm architecture.                                         | 48 |

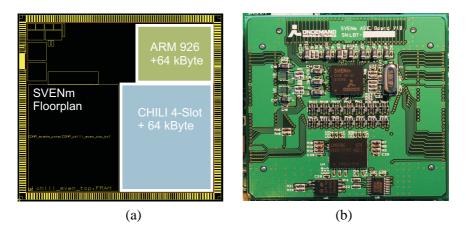

| 4.5  | Floorplan and board of the SVENm architecture.                               | 49 |

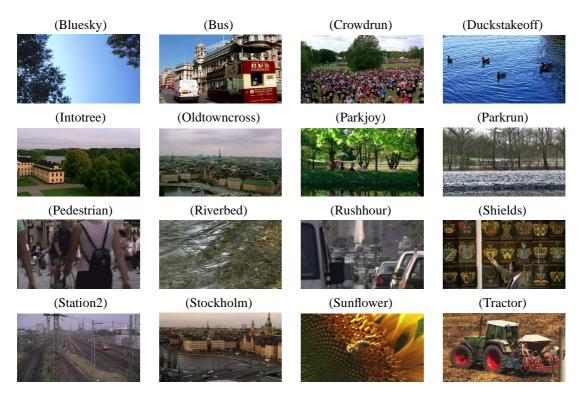

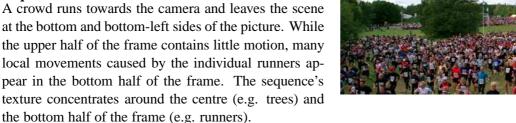

| 4.6  | Visualization of test sequences used in work.                                | 51 |

| 4.7  | GOP-Coding of a sequence with 25 frames.                                     | 52 |

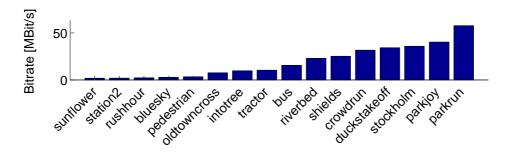

| 4.8  | Bitrates of the 16 test sequences coded at a Y-PSNR of 40 db                 | 53 |

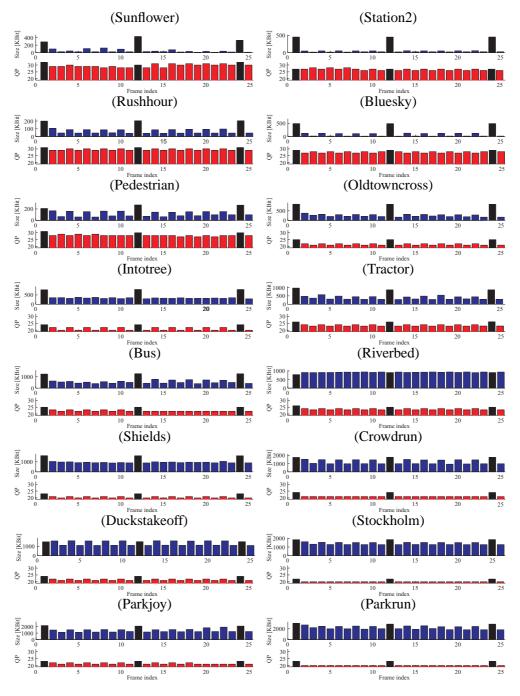

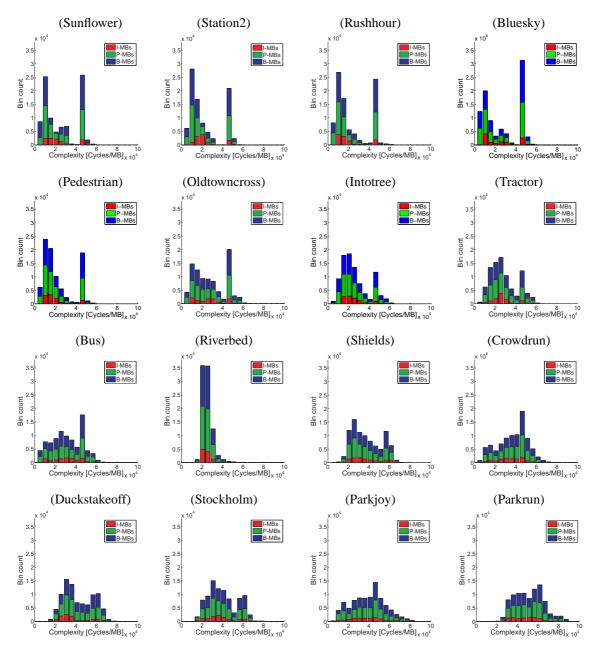

| 4.9  | Dynamic variations in the decoding time of individual macroblocks            | 57 |

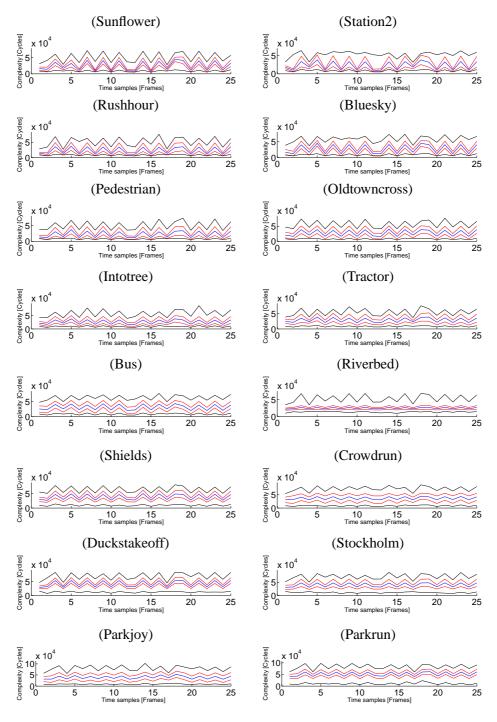

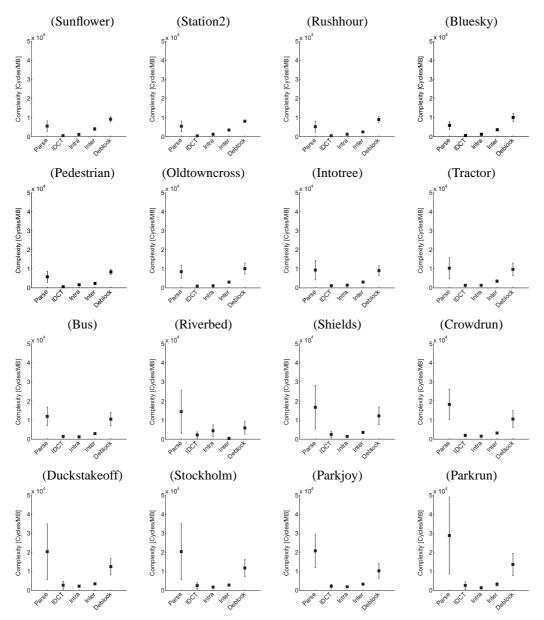

| 4.10 | Dynamic variations in the runtime of H.264's functional blocks.            | 59 |

|------|----------------------------------------------------------------------------|----|

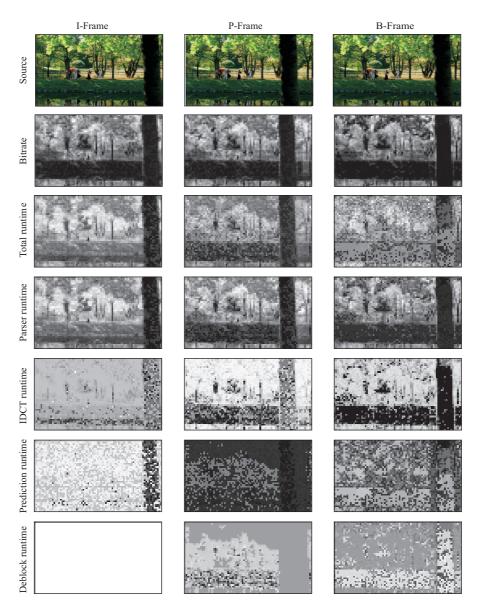

| 4.11 | Visualization of runtime complexity for the individual MBs of I/P/B-frames | 61 |

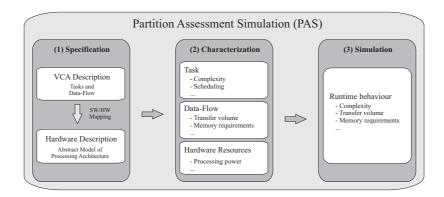

| 5.1  | The Partition Assessment Simulation (PAS)                                  | 64 |

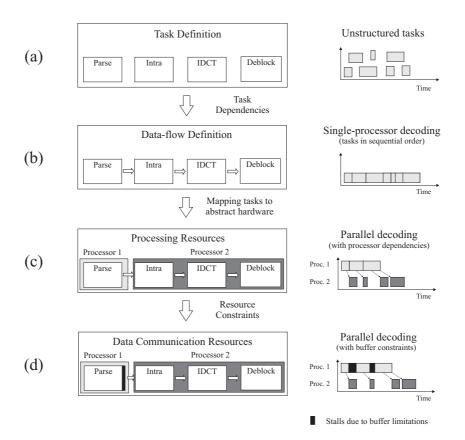

| 5.2  | System specification in the PAS                                            | 66 |

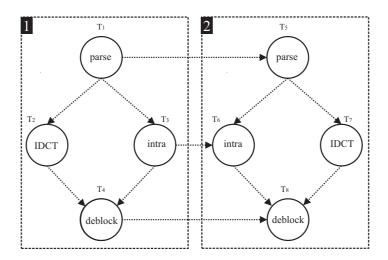

| 5.3  | Simple dependency graph for two macroblocks' decoding tasks.               | 68 |

| 5.4  | Sequential task order for a macroblock's decoding tasks.                   | 69 |

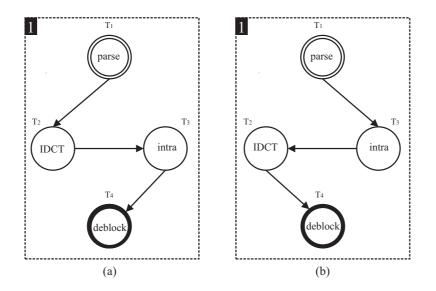

| 5.5  | Mapping of VCA graph onto hardware.                                        | 71 |

| 5.6  | Algorithm for simulating parallel task execution in a VCA                  | 74 |

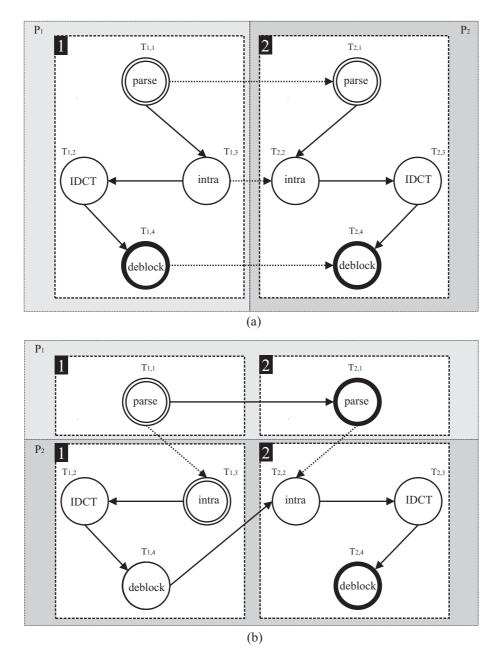

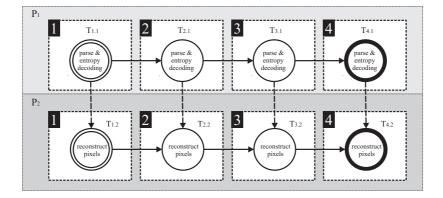

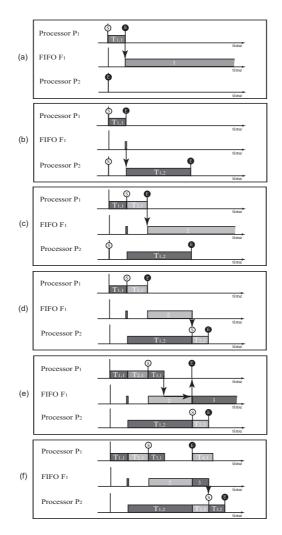

| 5.7  | Functional partitioning of four macroblocks.                               | 79 |

| 5.8  | Visualisation of the internal simulation process in the PAS                | 80 |

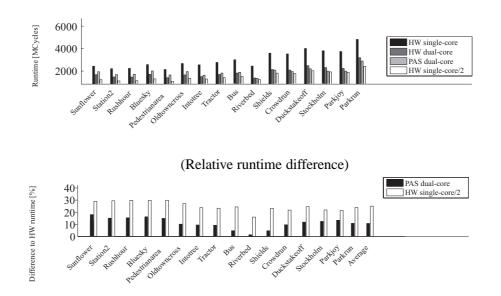

| 6.1  | Relative and absolute runtime differences when calibrating the PAS         | 85 |

| 6.2  | Relative runtime differences in percent during PAS calibration.            | 86 |

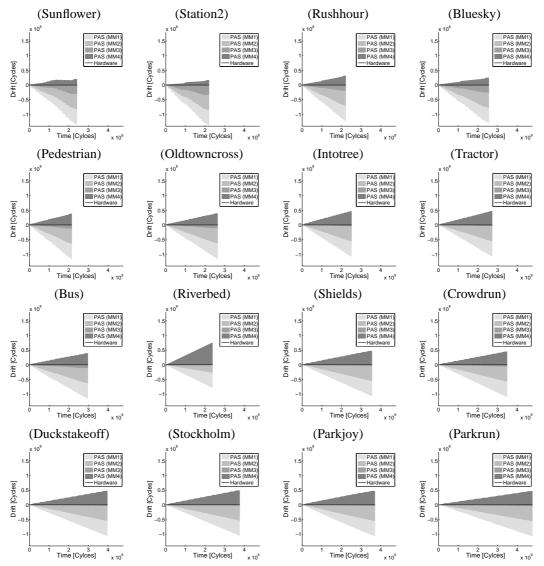

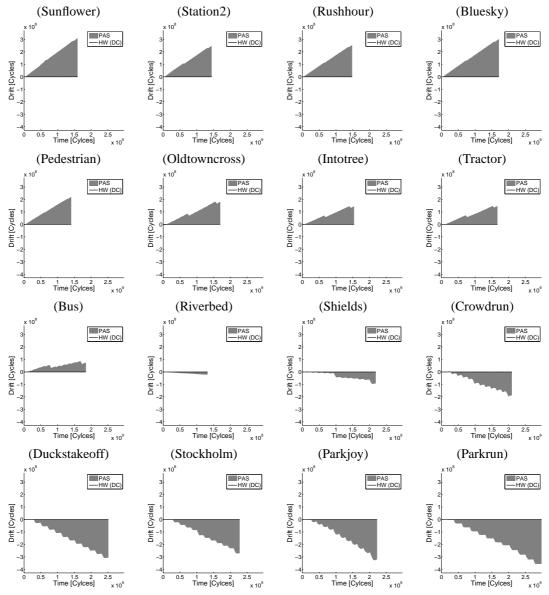

| 6.3  | Absolute runtime differences in clock cycles during PAS calibration.       | 87 |

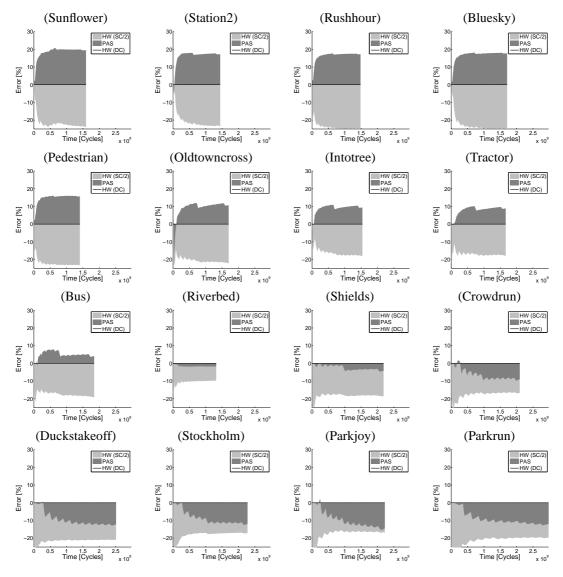

| 6.4  | Absolute runtime differences during PAS verification.                      | 88 |

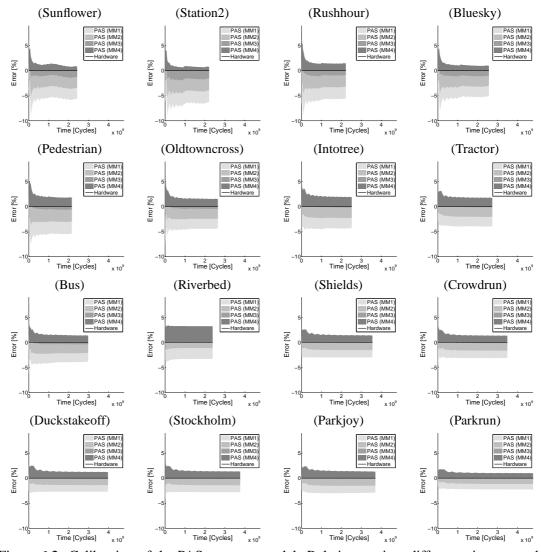

| 6.5  | Relative runtime differences during PAS verification.                      | 89 |

| 6.6  | Absolute runtime differences during PAS verification.                      | 90 |

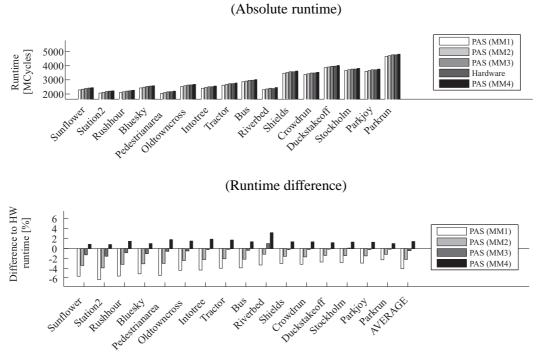

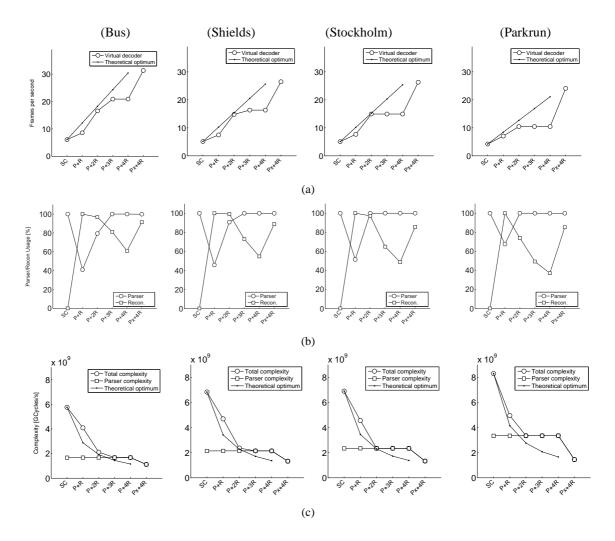

| 6.7  | Runtime of the simulated decoder partitioning approaches                   | 92 |

|      |                                                                            |    |

## **List of Tables**

| 2.1 | Example of dynamic function trace profiling.                         | 11  |

|-----|----------------------------------------------------------------------|-----|

| 4.1 | Profile for the tasks of the decoder's individual functional blocks. | 42  |

| 4.2 | Transition table of a state machine.                                 | 43  |

| 4.3 | Macroblock-based H.264 profile information.                          | 45  |

| 4.4 | Detailed size and quantisation values for the test sequences' frames | 54  |

| 4.5 | Complexity dynamics during the decoder's runtime                     | 56  |

| A.1 | Test sequences 1 to 4                                                | 100 |

| A.2 | Test sequences 5 to 8                                                | 101 |

| A.3 | Test sequences 9 to 12                                               | 102 |

| A.4 | Test sequences 13 to 16                                              | 103 |

|     |                                                                      |     |

# Abbreviations

| AI     |                                                           |

|--------|-----------------------------------------------------------|

| ASLI   |                                                           |

| BB     |                                                           |

|        | Context Adaptive Binary Arithmetic Coding                 |

| CAVLC  |                                                           |

| CFG    | 1                                                         |

| DAG    | 5 1                                                       |

| dB     |                                                           |

| DCC    |                                                           |

| DCT    |                                                           |

| DDP    | Data-Driven Profiling                                     |

|        | Data-Driven Profiling Library                             |

| DMA    | Direct Memory Access                                      |

| DPCM   | Differential Pulse Code Modulation                        |

| DR     | Dependency Rules                                          |

| FAF    | FIFO Assignment Function                                  |

| FB     | Functional Block                                          |

| FIFO   | First-In-First-Out buffer                                 |

| fps    | frames per second                                         |

| FSM    | Finite-state Machine                                      |

| GOP    | Group Of Pictures                                         |

| HVS    | Human Visual System                                       |

| HW     |                                                           |

| ICACHE | Instruction Cache                                         |

| IDCT   | Inverse Discrete Cosine Transform                         |

| IEC    | International Electrotechnical Commission                 |

| IP     | Instrumented Profiling                                    |

|        | International Organization for Standardization            |

| ISS    |                                                           |

| ITU    | International Telecommunication Union                     |

| ITU-T  | International Telecommunication Union - Telecommunication |

| kB     |                                                           |

| LoP    | 5                                                         |

| MAF    |                                                           |

|        |                                                           |

| MB     | Macroblock                                                       |

|--------|------------------------------------------------------------------|

| MCP    | Motion-compensated prediction                                    |

| mDDR   | Mobible Double Data Rate Memory                                  |

| MoE    | Model of Execution                                               |

| MSE    | Mean Square Error                                                |

| MV     | Motion Vector                                                    |

| NAL    | Network Abstraction Layer                                        |

| OoE    | Order of Execution                                               |

| PAF    | Processor Assignment Function                                    |

| PAS    | Partition Assessment Simulation                                  |

|        | Pushdown Automaton                                               |

| PSNR   | Peak Signal-to-Noise Ratio                                       |

|        | Processing Unit                                                  |

| -      | Quantisation Parameter                                           |

|        | Reduced Instruction Set Computer                                 |

|        | Simulation-based Runtime Prediction                              |

|        | Single Instruction Multiple Data                                 |

|        | Software Instrumentation Tool                                    |

|        | System-on-Chip                                                   |

|        | Shared Random-access Memory                                      |

|        | Sequential Task Order                                            |

| SW     |                                                                  |

|        | Transport Stream                                                 |

|        | Unique Identifier                                                |

|        | Virtual Architecture                                             |

|        | Video Coding Application                                         |

|        | Video Coding Layer                                               |

|        | Video Coding System                                              |

|        | Very High Speed Integrated Circuit Hardware Description Language |

|        | Very High Speed Integrated Circuit                               |

|        | Very Long Instruction Word                                       |

|        | Virtual System Definition                                        |

| Y-PSNK | Peak Signal-to-Noise Ratio of the luma channel                   |

## CHAPTER

## Introduction

#### **1.1** Design of parallel video coding architectures

State-of-the-art video standards such as H.264 [ITU12] are used in a wide range of industrial and consumer applications. This includes for example digital television broadcasting, video surveillance and video conferencing. Compared to preceding video coding standards such as MPEG-2 and MPEG-4 SP/ASP, improved coding efficiency could be reached by introducing more advanced pixel processing algorithms (e.g. quarter-pixel motion estimation, integer-based block transforms) as well as by the use of more sophisticated algorithms for predicting syntax elements from neighbouring macroblocks (e.g. context-adaptive variable-length coding). These new coding tools result in significantly increased CPU and memory loads required for coding a video stream. In environments of limited processing power such as embedded systems, the high computational demands pose a challenge for practical video coding implementations [FG01]. Multi-core System-on-Chip (SoC) design provides an elegant solution to overcome these performance limitations.

A SoC design combines multiple components such as processors and memories on a single chip. The usage of existing and well-tested components can reduce the costs and the developing time and results in a short time-to-market. The programmability of most SoCs allows later modifications of the algorithm's software which offers high flexibility and is of prime importance for video coding. For example, for adapting the software when a new extension of a video standard becomes available or to run different video coding algorithms on the same platform.

The high computational demands of state-of-the-art video coding application (VCAs) pose serious challenges on current SoC architectures. A natural way to tackle this problem is the use of multi-core systems. However, the efficient distribution of video coding algorithms among multiple processing units (PUs) is a non-trivial task. For using the available processing resources efficiently, an equally balanced distribution of the coding tasks onto the hardware units must be found. The system designer has to consider data dependency issues as well as intercommunication and synchronisation between the PUs. Furthermore, the resource limitations in an embedded environment such as low computational power, small-sized memories and low bus bandwidth require an efficient software design. A parallel VCA approach must be able to work under these resource restrictions.

#### **1.2** Motivation and objectives

A major source for uncertainty within most VCA designs is that the software development and partitioning is typically addressed at a late phase of the SoC design. At this stage, significant resources already went into the system's hardware design and integration and changes are expensive and only possible in a limited scope. However, from what has been outlined above, multiple questions arise already at early design phases of a multi-core video processing system when the components of the SoC design are chosen:

- 1. Can we reach the performance requirements of the VCA on the available hardware?

- 2. What hardware is required by the VCA to handle a specific set of video streams?

- 3. What is the optimal VCA partitioning for using the architecture's resources most efficiently?

In previous work, the first two questions have been widely discussed for single-core architectures. Various complexity estimation and runtime prediction techniques with their respective advantages and disadvantages have been proposed. We describe existing complexity and runtime estimation techniques and their strengths and weaknesses in detail in Section 2. However, the existing profiling techniques for single-core VCAs are only suitable to a limited extent for addressing multi-core SoC design for parallel video coding applications in an efficient way. They typically provide coarse profiling information on the larger functional blocks (e.g. the absolute runtime spent in a decoding function and all sub-functions) but do not provide means for efficiently analysing the runtime complexity of an VCA at the level where the parallelisation would be implemented. This makes it hard to exploit the available profiling information when making predictions about the single-core VCA runtime performance on a multi-core architecture.

Addressing this weakness of existing profiling techniques is one major objective of this thesis. We provide a method to efficiently derive runtime information from single-core VCAs that typically affects the system designers choice of parallelisation. For example, detailed execution times for the video coding elements that are processed during the VCA execution and runtime variation of individual functional blocks are provided. We introduce a new complexity analysis technique that equips system designers with a toolset to extract runtime information at a level where parallelisation will take place later on. We extend traditional complexity estimation and profiling techniques in a way that enables more detailed analysis of a VCA's parallel execution behaviour. A special focus shall be given to the hierarchical data structures and functional blocks of VCAs. They determine where parallelisation mechanisms can be integrated within the VCA and must be considered carefully when analysing parallel execution behaviour.

The third question above introduces the need for predicting the runtime of "virtual" VCA partitionings, which typically is not accurately possible with traditional analytical models or too time- and labor-intensive using existing hardware simulation techniques. Prediction techniques

that base their runtime estimation on formal algorithm definitions (i.e. analytical runtime prediction techniques) or runtime observations from single-core implementations typically cannot consider parallel task concurrency and inter-task dependencies appropriately when estimating the complexity of a VCA in a parallel architecture configuration. More powerful prediction techniques that can simulate the hardware and software execution for virtual platforms typically require an already partitioned VCA implementation. Estimating the runtime performance of a parallel VCA's software partitioning without starting the labor-intensive implementation work is not possible. Furthermore, many simulation techniques require circuit-based hardware simulation which is very time-intensive. These limitations due to (i) labor- and time-intensive implementation aspects and (ii) time-intensive simulation limit the possibilities to estimate parallel VCA designs at an early stage of the design process.

This thesis tackles these problems in two steps. Firstly, we will introduce a modelling technique that allows the system designer to describe a VCA in an abstract way. We will combine *complexity estimation* and *virtual prototyping* techniques for describing "virtual" architecture configurations. A framework that allows virtual prototyping of abitrary software and hardware architectures for video coding that overcomes the need for implementing software or hardware partitionings is developed. Secondly, a simulation framework that enables the simulation of this "virtual" platform is introduced. It enables the system designer to obtain accurate estimates for the runtime complexity of the VCA when decoding a video stream.

In summary, the capabilities of current runtime analysis and prediction techniques are typically not suitable for predicting the runtime behaviour of single-core VCAs on a parallel architecture in an accurate and fast way. The techniques introduced in this thesis equip the system designer with a new toolset for tackling this problem and to reduce the technological risk during the system design.

#### **1.3** Contributions

The methods and applications contributed in this work shall enable system designers to efficiently explore the behaviour of VCAs on parallel hardware architectures. The main contributions of this thesis are summarized in the following:

- We investigate what information is provided by traditional single-core profiling techniques and introduce an innovative technique for mapping this information onto the functional blocks and coding elements of VCAs. This Data Driven Profiling (DDP) mapping technique enables the system designer to derive essential information on the VCA's execution behaviour and for making assumptions about the runtime behaviour of the VCA on a parallel hardware platform.

- We introduce a modelling technique for describing VCAs' coding elements, functional tasks and the data-dependencies between these tasks. We introduce a high-level simulation methodology, the Partition Assessment Simulation (PAS), for the modelling and simulation of parallel VCA hardware architectures. This methodology estimates the performance of a VCA for arbitrary virtual hardware and software configurations and enables design space explorations of parallel video processing architectures.

- We provide a simulator for analysing implementation aspects of the PAS methodology. We verify the methodology on an existing hardware architecture and analyse its accuracy for a real-world H.264 decoder scenario.

- We perform design space exploration for an H.264 decoder and evaluate the runtime performance of various decoder partitionings on a virtual architecture.

We believe that the proposed high-level methods for estimating the computational complexity of multi-core video coding systems is preferable over existing techniques, since these are typically not suited for the complex nature of multi-core systems. They can often not consider the concurrency and inter-processor dependencies inherent to multi-core systems. A valid alternative to our method is represented by the simulation-based prediction techniques described in Section 2.3. These methods can handle concurrency and inter-processor dependencies. However, for simulating the runtime behaviour of a parallel VCA, these approaches typically require a well-defined or completely implemented architecture and a partitioned software (i.e. low-level specification of the interfaces and components). Due to the vast amount of work that is required to implement each VCA partitioning approach, early high-level complexity estimations are difficult to realize and the flexibility to explore many different software designs is limited. The methodology introduced in our work aims to enable fast design space exploration and to estimate complex multi-core video coding systems in a flexible, time- and labor-efficient way.

#### **1.4 Resulting publications**

The following publications in scientific journals and at conferences have resulted from the work presented in this thesis:

#### Journals

- <u>F. H. Seitner</u>, M. Bleyer, M. Gelautz, R. M. Beuschel: Evaluation of data-parallel H.264 decoding approaches for strongly resource-restricted architectures, *Journal on Multimedia Tools and Applications*, Springer, volume 53, issue 2, pages 431-457, 2011.

- <u>F. H. Seitner</u>, M. Bleyer, M. Gelautz, R. M. Beuschel: Development of a high-level simulation approach and its application to multi-core video decoding, *IEEE Transactions on Circuits and Systems for Video Technology*, volume 19, issue 11, pages 1667-1679, 2009.

#### **Conferences with proceedings**

- <u>F. H. Seitner</u>, M. Bleyer, R. Schreier, M. Gelautz: Evaluation of data-parallel splitting approaches for H.264 decoding, *Proc. of the 6th International Conference on Advances in Mobile Computing and Multimedia*, pages 40-49, Linz, 2008. (oral presentation)

- <u>F. Seitner</u>, M. Bleyer, M. Gelautz: Development of multi-core video decoding platforms based on high-level architecture simulations, *Proc. of the Junior Scientist Conference*, pages 71-72, Vienna, 2008. (oral presentation)

- <u>F. Seitner</u>, J. Meser, G. Schedelberger, A. Wasserbauer, M. Bleyer, M. Gelautz, M. Schutti, R. Schreier, P. Vaclavik, G. Krottendorfer, G. Truhlar, T. Bauernfeind, P. Beham: Design methodology for the SVENm multimedia engine, *Proc. of the Austrochip 2008*, page 113, Linz, 2008. (poster presentation)

- <u>F. H. Seitner</u>, R. M. Schreier, M. Bleyer, M. Gelautz: A high-level simulator for the H.264/AVC decoding process in multicore systems, *Electronic Imaging*, SPIE, volume 6821, pages 5-16, San Jose, 2008. (oral presentation)

- <u>F. H. Seitner</u>, R. M. Schreier, M. Bleyer, M. Gelautz: A macroblock-level analysis on the dynamic behaviour of an H.264 decoder, *IEEE International Symposium on Consumer Electronics*, pages 1-5, Dallas, 2007. (oral presentation)

#### Patents

• R. Schreier, <u>F. Seitner</u>: Method and apparatus for encoding and decoding of video streams, *US Patent*, Application number 20080152014, filed 12/2007.

#### **Technical reports**

- <u>F. H. Seitner</u>, R. M. Schreier, M. Bleyer, T. Albrecht, M. Gelautz: Analysis of video algorithms, *FIT-IT Project VENDOR*, WP2.2, Vienna University of Technology, 2007.

- <u>F. H. Seitner</u>, R. M. Schreier, M. Bleyer, T. Albrecht, M. Gelautz: Literature survey of state-of-the-art video algorithms, *FIT-IT Project VENDOR*, WP2.1, Vienna University of Technology, 2007.

#### 1.5 Organization

The content of this thesis is organized into seven chapters. The current chapter provided a general overview about the motivation and contributions of this work. In the following, we briefly describe the chapters in the remainder of this thesis and provide links to the publications listed before.

- In Chapter 2 we provide an overview of existing complexity estimation and runtime profiling techniques. We discuss the individual techniques and explain their limits when it comes to multi-core architecture design and design space exploration. The main text of this chapter is taken from our published papers [SSBG11, SSBG09].

- Chapter 3 outlines the fundamentals of hybrid video coding standards. In this chapter, we derive the characteristics of hybrid video coding algorithms and describe the design challenges of parallel video coding systems. The main text of this chapter is taken from our published papers [SBSG08, SSBG11, SSBG08], with more details and additional explanations.

- We exploit these characteristics in Chapter 4 to introduce a novel runtime profiling method. It addresses various short-comings of traditional dynamic profiling techniques and enables the correlation of runtime complexity with specific coding elements and functional blocks of a hybrid video coding algorithm. This provides important insights into the complexity and can be exploited for identifying bottlenecks and potential challenges in the design of parallel coding solutions at an early stage of the development. The main text of this chapter is primarily a compilation of our published papers [SBSG08,SSBG11,SSBG09,SSBG07], with additional results and experiments.

- In Chapter 5, we introduce a virtual prototyping methodology, the Partition Assessment Simulation (PAS) technique. We explain the design goals and theoretic fundamentals and describe an implementation of this prototyping concept. The main text of this chapter is primarily a compilation of our published papers [SBSG08, SSBG11, SSBG09], with additional details and explanations of the PAS concept and its implementation.

- In Chapter 6, we analyse the PAS in more detail and evaluate and verify this technique's accuracy using a real-world H.264 decoder. We use the PAS for modelling a virtual VCS for demonstrating the possibilities towards efficient design space exploration using examples of functional as well as data-parallel partitioning approaches. The main text of this chapter is primarily a compilation of our published papers [SSBG11, SSBG09], with additional experiments and results.

- Chapter 7 provides conclusions and an outlook on future work. The main text of this chapter is primarily a compilation of our published papers [SSBG11, SSBG09].

# CHAPTER 2

# Prior work on complexity and runtime estimation

Obtaining information about the runtime complexity of an algorithm is typically highly important when developing the hardware or software components that compute the algorithm's individual processing steps. Accurate performance analysis supports important stages of a development process such as the system design, optimisation, functional verification and testing. For estimating runtime complexity, various prediction techniques have been developed. We can divide the existing estimation techniques into three major groups: the analytical, the profiling-based and the simulation-based approaches. In the Sections 2.1, 2.2 and 2.3, we will describe these techniques in more detail. Section 2.4 provides an overview of high-level design exploration techniques. In Section 2.5, we put the techniques contributed in this thesis in the context of prior work.

#### 2.1 Analytic runtime prediction

Based on the fundamentals of the Computational Complexity Theory [FH03], advanced analytic methods for analysing an algorithm's complexity have been introduced. For example, the Static Algorithm Analysis [PK89] and Worst Case Execution Time (WCET) estimation [LM95, MML97] have been evolved. These techniques analyse formal definitions of an algorithm, for example its source code, for estimating the algorithm's computational complexity.

Most theoretic complexity approaches describe the complexity of an Algorithm A using an *instance-based* complexity measure  $T_A[\cdot]$  [ST09]. This measure defines the complexity  $T_A[x]$  of an Algorithm A for an input instance x. For each Algorithm A, an input domain  $\Omega$  containing all possible input instances x is provided. For a finite input domain  $\Omega$ , this complexity measure defines a  $|\Omega|$  dimensional vector (i.e. each element in this vector represents the complexity  $T_A[x]$  of an input instance  $x \in \Omega$ ). Depending on the number of input instances  $|\Omega|$ , the effort for estimating and describing an algorithm's complexity strongly varies.

For a more specific analysis of an algorithm's complexity, the input domain  $\Omega$  is usually viewed as the union of a set of sub-domains  $\{\Omega_1, \Omega_2, ..., \Omega_n\}$ . Each sub-domain  $\Omega_i$  represents all input instances of size *i*. For example, in the context of sorting algorithms,  $\Omega_i$  refers to the set of all tuples containing *i* elements.

Based on these sub-domains, the complexity of an algorithm A is often described as a function of the input size of the problem A aims to solves. We can define a scalar  $T_A(n)$  which summarizes the complexity  $T_A[x]$  for all instances  $x \in \Omega_n$ . In our example with the sorting algorithm,  $T_A(n)$  describes the complexity of sorting an input instance with n elements. In *Theoretical Computer Science*, the WCET is one of the most commonly used metrics for summarizing the complexity of an algorithm. The WCET of Algorithm A can be derrived in the following way:

$$WCET_A(n) = \max_{x \in \Omega_n} T_A[x]$$

(2.1)

It describes the maximal execution time of an Algorithm A processing an input instance consisting of a tuple of n elements.

Runtime prediction based on static analysis measures has multiple shortcomings. First, the execution paths of most algorithms depend on the data values of the input instances. For example, input-dependent recursions and branches in an algorithm can cause *dynamic* variations in an algorithm's execution path and its runtime. Consequently, theoretic complexity measures such as the WCET do not necessarily reflect an algorithm's runtime behaviour under real working conditions [ST09].

Second, analytical complexity predictions cannot easily be bound to a specific hardware platform. The runtime of an algorithm depends on the processing resources of the executing platform (e.g. instruction set, processing pipeline, clock rate). An algorithm that performs well in theory not necessarily does this on a platform with physical processing resources and architectural limitations.

#### 2.2 Runtime prediction based on dynamic profiling

Dynamic profiling aims to address the limitations of analytical runtime prediction by observing the execution of an algorithm on a physical *reference platform*<sup>1</sup>. Most hardware platforms provide tools for observing program execution during runtime and for *measuring* the runtime of executing programs. Prediction techniques based on dynamic profiling exploit the knowledge gained from these *complexity measurements*. Based on observations of the execution behaviour of a Program P on a reference platform R, the system designer makes assumptions about the program's execution behaviour.

Similar to the input domain  $\Omega$  used in analytical runtime prediction, runtime measurements obtained via dynamic profiling aim to reflect the complexity for a range of input instances. For example, for a video decoder the bitrate of a coded input stream typically has a strong impact on the runtime complexity. This can be used for defining input sub-domains  $\{\Omega_1, \Omega_2, ..., \Omega_n, ...\}$  for

<sup>&</sup>lt;sup>1</sup>In the context of this work, we use the term program to refer to an algorithm's source code or binary representation on a physical hardware platform.

Figure 2.1: A simple control flow graph (CFG): Each node represents a basic block (BB) of a program. The directed edges between the nodes represent the jumps from one BB to another BB. (a) A CFG with three BBs: Block A represents the first BB of the program. After Block A either Block B or Block C are executed. Block C is the last BB executed within the program. (b) A CFG with three blocks and a loop between Block A and B.

our VCA where each sub-domain represents the decoding complexity of video streams within a well-defined bitrate range. For obtaining the runtime complexity of a subdomain  $\Omega_i$ , we would profile multiple input streams within the domain's bitrate range. The longest or average execution times a VCA requires to decode these streams would reflect the WCET and the average runtime complexity for this input sub-domain, respectively.

In practice, dynamic profilers regard a program as a set of Basic Blocks (BBs). The term Basic Block has been introduced by Allen [All70] and refers to a linear sequence of program instructions that has no jump instructions contained within it. The first and last instructions of each basic block are called *entry point* and *exit point*, respectively. For entering a BB, the entry point of this BB may be entered from one or more exit points within the program.<sup>2</sup>

BBs are usually the basic units a compiler works with during the optimisation phase and also enable profiling of the individual program regions. The program is regarded as a graph where the BBs form the graph's nodes and the jumps between the BBs the transitions between the nodes. These graphs are called Control Flow Graphs (CFGs). In Figure 2.1a and 2.1b, we show two simple CFGs with three states each. In Figure 2.1a, a transition from State A to State B as well as to State C is possible. In State B, only a transition to State C is possible. Figure 2.1b contains a loop where the States A and B can be executed multiple times before reaching the final State C.

The execution time of a Program P is the sum of execution times of all its BBs multiplied by the number of executions of the BBs. We can compute the execution time  $t_P$  of Program Pthat consists of n BBs  $(BB_1..BB_n)$  in the following way:

$$t_P = \sum_{i=1}^{n} t_{BB_i} * f_{BB_i}$$

(2.2)

<sup>&</sup>lt;sup>2</sup>A BB Y that is entered after the execution of a BB X is called a *successor* of BB X. BB Y is called the *predecessor* of BB X.

The terms  $t_{BB_i}$  and  $f_{BB_i}$  refer to the execution time and the number of executions of  $BB_i$ , respectively.

In practice, dynamic profiling techniques can be classified into two major groups: *Statistical* and *instrumented* profiling techniques. In the following sections, we describe these techniques in more detail.

#### 2.2.1 Statistical profiling

In statistical profiling, the program counter (PC) of a program is observed during the program's execution. The value of the PC represents the position where the execution of the program currently takes place. By sampling the PC in regular time intervals, conclusions about the executed parts of the program and the frequency at which these parts are executed can be derived. The time interval between each sample (i.e. the *sampling period*  $T_S$ ) is typically known to the profiling environment. It is measured in seconds and is the inverse of the *sampling frequency*  $F_S$  (i.e. the number of samples taken per second):

$$T_S = \frac{1}{F_S} \tag{2.3}$$

Based on the total number of samples  $n_P$  that lie within memory blocks assigned to a Program P, we can estimate the total runtime  $\hat{t}_P$  of this program:

$$\hat{t}_P = T_S * n_P \tag{2.4}$$

In this estimation, each sample is counted as a period of  $T_S$  seconds.

Since the memory location of each BB of the program is typically known, we can unambiguously assign each PC sample to a BB. This allows us to derive the number of samples  $n_{BB_i}$  that occurred within a block  $BB_i$  during the execution of P and to estimate the total runtime  $\hat{t}_{BB_i}$  spent in  $BB_i$  during the program's execution:

$$\hat{t}_{BB_i} = \hat{t}_P * \frac{n_{BB_i}}{n_P} \tag{2.5}$$

The factor  $\frac{n_{BB_i}}{n_P}$  is the percentage of the BB's runtime on the total runtime.  $\hat{t}_P$  is the total runtime of Program P

Note that  $\hat{t}_{BB_i}$  is statistically approximated and does not necessarily represent the exact runtime of  $BB_i$ . Especially, when using a low sampling frequency  $F_S$  and when measuring small and rarely executed BBs, the number of observed samples can strongly vary between measurements. Furthermore, no accurate information on the number of executions of each BB during the execution of P can be obtained by statistical profiling techniques.

#### 2.2.2 Instrumented profiling

Instrumented Profiling (IP) techniques extend the target progam with additional program instructions [GKM82, BL94]. *Instrumentation* refers to the task of inserting instructions for profiling

|    | when the function is entered and enter a ferrer of the promet. |                         |  |  |  |  |  |

|----|----------------------------------------------------------------|-------------------------|--|--|--|--|--|

| 1  | CALL StartH264Decoder                                          | time = $1$              |  |  |  |  |  |

| 2  | CALL DecodeFrame                                               | <b>time</b> = 2         |  |  |  |  |  |

| 3  | CALL DecodeMacroblock                                          | $\mathbf{time} = 1000$  |  |  |  |  |  |

| 4  |                                                                |                         |  |  |  |  |  |

| 5  | RETURN                                                         | $\mathbf{time} = 10000$ |  |  |  |  |  |

| 6  |                                                                |                         |  |  |  |  |  |

| 7  | CALL DecodeMacroblock                                          | $\mathbf{time} = 10020$ |  |  |  |  |  |

| 8  |                                                                |                         |  |  |  |  |  |

| 9  | RETURN                                                         | time = 23000            |  |  |  |  |  |

| 10 | CALL DecodeMacroblock                                          | time = 23001            |  |  |  |  |  |

| 11 |                                                                |                         |  |  |  |  |  |

| 12 | RETURN                                                         | time = 35000            |  |  |  |  |  |

| 13 | RETURN                                                         | time = 35001            |  |  |  |  |  |

| 14 | RETURN                                                         | time = 35002            |  |  |  |  |  |

|    |                                                                |                         |  |  |  |  |  |

Listing 2.1: Example of a dynamic runtime trace: For each execution of a function, the times when the function is entered and exited are retrieved by the profiler.

| Function name    | Calls | Gross runtime |        | Net runtime |      | Net runtime (Cycles/Call)) |       |       |

|------------------|-------|---------------|--------|-------------|------|----------------------------|-------|-------|

|                  |       | Cycles        | %      | Cycles      | %    | Min.                       | Avg.  | Max.  |

| StartH264Decoder | 1     | 35002         | 100.00 | 2           | 0.1  | 2                          | 2     | 2     |

| DecodeFrame      | 1     | 35000         | 99.9   | 1019        | 2.8  | 1019                       | 1019  | 1019  |

| DecodeMacroblock | 3     | 33981         | 97.1   | 33981       | 97.1 | 9001                       | 11327 | 12981 |

Table 2.1: Dynamic profile: For a VCA consisting of three functions, the table provides the profiled gross and net runtimes. Additionally, the table shows the minimal, average and maximal runtime for each function call. More details are provided in Section 2.2.2.

purposes into a program. These instructions collect information about the behaviour of the program during runtime such as the program's execution path. Instrumented Profiling at BB level can gather information about the time when a BB is entered and exited, the frequency  $f_{BB_i}$  and duration  $d_{BB_i}$  of a basic block  $BB_i$ .

The output of an instrumented profiler typically contains a stream of recorded events such as calls to the BBs of a program. This set of events is referred to as the profiler's *trace*. For a more intuitive interpretation by the system designer, modern profiles typically maps the events of a trace to the program's *functional level* (i.e. source code functions).

Listing 2.1 shows an example of a simple trace at functional level of a VCA. In this example, the VCA consists of three functions: *StartH264Decoder*, *DecodeFrame* and *DecodeMacroblock*. The trace provides insights when a function  $f_j \in F_{VCA}$  is called or left. We refer to function  $f_j$  as *callee* and the function which called  $f_j$  as *caller*.

Dynamic profilers typically provide a summary of a trace's observations (i.e. the *profile*). A functional profile of the trace from Listing 2.1 is given in Table 2.1. This table provides a summarized complexity information that can be exploited for optimising the VCA's computational expensive parts. For each function, information such as the number of function calls, the absolute and relative runtime in cycles and percentage of the total program runtime are typically

obtained. Gross runtime (i.e. cumulative runtime of all functions that occur during a function execution), net runtime (=function's gross runtime without runtime spent for sub-function execution) and statistical information on minimum, average and maximum runtime per function call enable us to concentrate on runtime expensive functions during the optimisation. Time-intensive optimisations (e.g. hardware-dependent code optimisations using assembler code) for functions with insignificant complexity can be avoided.

However, placing profiling instructions inside a target program can cause changes in the runtime performance. Additional profiling instructions are executed during the program execution which increases the runtime complexity. The increased number of instructions can further cause changes in the platform's instruction caching strategy and result in significant changes in the total runtime. Modern architectures provide efficient hardware support for reducing the impact of instrumentation on a program's runtime. They provide specific instructions for tracing the program's execution with a minimal execution overhead. Furthermore, profiles have been evolved that estimate the complexity overhead caused by the profiling and correct the profiling results based on this.

Despite the advanced hardware support of instrumented profiling, the additional profiling instructions can have a significant impact on the compile process and the resulting binary. Impacts on the program runtime behaviour occur. For keeping this impact low, hybrid profiling techniques based on statistical sampling (Section 2.2.1) and IP are used in practice. This keeps the instrumentation overhead low and results in more accurate runtime measurments. For example in gprof [GKM82], instrumentation is used for collecting the information about function frequency and function entry/exit times and statistical sampling for measuring the runtime.

#### Instrumentation of profiling instructions

For instrumentation, manual as well as automatic techniques exist. *Manual Instrumentation* refers to the manual insertion of the profiling instructions into a target program's source code. This is typically used for profiling and debugging specific parts of a program. The manual insertion of profiling instructions can be highly labor- and time-intensive and for more extensive profiling, *Automatic Instrumentation* (AI) techniques have evolved.

AI automatically inserts profiling instructions at relevant positions of the program. Various AI techniques have been introduced that differ in the way the insertion of the profiling instructions into the program is done. *Automatic Source Level Instrumentation* (ASLI) analyses the source code of a program and inserts the profiling instructions directly into the program's source code (i.e. before the program's compilation into binary code). An example of ASLI has been introduced by Ravasi and Mattavelli [RM05]. They have developed the Software Instrumentation Tool (SIT) which extends traditional C source code to *instrumented* C++ classes. This instrumentation provides detailed information on the number of arithmetic and memory load/store operations executed during a program's execution.

In a similar spirit, the ATOMIUM tool [NCK<sup>+</sup>96] performs high-level transformation of C code. The focus of this tool lies on memory analysis. The *Data Transfer and Storage Exploration* methodology (DTSE) is introduced. Based on this methodology, C code can be optimised in terms of execution time, memory size and power consumption.

Apart from AI of the program's source code, techniques for instrumenting the binary of a program exist. This instrumentation can take place during the compiling [GS04] as well as the binary linking [SE94] stages of a program. Furthermore, dynamic binary analysis tools such as Valgrind [NS07], PIN [LCM<sup>+</sup>05] and DynamoRIO [BGA03] exist that instrument programs at runtime.

#### 2.3 Simulation-based runtime prediction

In Simulation-based Runtime Prediction (SBRP), a *simulator* mimics the physical hardware platform and its behaviour over time. This enables the designer to model a hardware platform before it is physically created and to simulate a program's runtime execution on this "virtual" platform. Since the hardware is simulated, very detailed observation of the program's runtime behaviour on this platform is possible.

The existing simulation approaches can be divided into four major groups: *Hardware simulation, instruction set simulation, HW/SW-codesign* and *high-level simulation techniques.*

#### 2.3.1 Hardware simulation techniques

For describing the hardware logic (i.e. the electronic circuits), the design and the temporal behaviour of a hardware design, Hardware Description Languages (HDLs) are typically used. Examples of HDLs are VHDL [VHD88], Verilog [TM91] and SystemVerilog [SDF06]. In contrast to software languages such as C, important characteristics of HDL languages are (i) the explicit notion of time and (ii) the capability to describe concurrent events in a formal way. Both characteristics are primary attributes of hardware and enable accurate specifications of circuits and physical hardware blocks. A simulator interprets the semantics of the HDL statements and mimics the behaviour of a hardware design's individual circuits over time.

The simulation of HDL descriptions allows the system designer to specify, test and verify the hardware logic before the design is physically built. However, HDL simulations of complex hardware designs are computationally very expensive and time consuming. This limits the ability to simulate the execution of complex software applications on an HDL-based hardware design simulator. Instruction Set Simulators are typically more suitable for this purpose.

#### 2.3.2 Instruction set simulation

An Instruction Set Simulator (ISS) is a program that simulates the execution of a program on a programmable processor. The system designer describes the individual registers, the operations and the decoding pipeline of this processor. The ISS mimics the "virtual" processor's progress over time by simulating the execution of the program's individual instructions in the decoding pipeline.

Compared to an HDL simulator, an ISS regards each register as a "virtual" variable. Detailed profilings about a program can be retrieved without simulating the underlying hardware logic [CK94, WR96]. This reduces the simulation complexity and hence the simulation time significantly. The simulation at a higher level of abstraction makes ISS computationally less expensive than HDL simulations and more suitable for analysing and developing complex software applications.

In [HS09], an accurate profiling tool based on ISS for fast and accurate performance, power, and memory access analysis of embedded systems is introduced. This approach simulates hard-ware and software at an instruction level which enables the exploration of different low-level hardware configurations setups.

#### 2.3.3 HW/SW-codesign

The flexibility of software (SW) design compared to hardware (HW) implementations have resulted in the development of advanced HW/SW-codesign methods such as described in [KM96, CLN<sup>+</sup>02, YYS<sup>+</sup>04, WPH<sup>+</sup>05]. These methods enable the systematic integration, testing and verification of new HW design implementations. Verified SW implementations typically serve as a starting point for HW/SW-Codesign techniques. Compared to a hardware design, implementing a complex algorithm in software has multiple advantages. This includes, for example, a faster and more flexibe development using high-level programming languages and easier correction of design errors. One prime intention of HW/SW-Codesign is the systematic transition from a functionally verified complex SW implementation to a corresponding HW design. This is typically done in the following way:

First, the system designer verifies the functional correctness of the SW implementation and the individual functional components using e.g. an ISS or another physical platform the SW can be compiled and executed on. Second, one SW component after the other is transferred into a corresponding HDL description and simulated using a hardware simulator. By connecting the HW simulator with the simulation environment where the SW verification has taken place, each HW component can be tested in the context of the whole implementation. The designer can find differences between the software and hardware implementation and verify the correctness of new HW blocks. For example, by comparing the data that is exchanged via the interfaces between the SW and the HW components or by comparing the results between the "pure" SW and the HW/SW design.

Apart from verification and migration from SW to HW, HW/SW-codesign approaches exist that target the modelling of virtual prototypes for new system designs. Examples are the OVPsim simulator [Agr09], the M5 simulator system [BDH<sup>+</sup>06] and the simulation platform Simics [MCE<sup>+</sup>02, VAG05]. Typically, multiple processor simulation models are connected with each other. By simulating parallel execution and inter-communication of the SW components running on these processors, these approaches mimic the parallel system's execution behaviour. They predict the real protoype's runtime behaviour and provide means for efficiently developing real-world design concepts. This enables evaluation and improvement of the design as well as investigation of design alternatives before a real and expensive prototype is built.

These simulators simulate the HW as well as the SW components of the system. However, these methods have two major shortcomings. First, the simulators often mimic the exact behaviour of each HW component (i.e. processor pipeline, caches, memory subsystems, etc.). This results in high computational complexity and limits the possibilities for simulating many HW and SW configurations. Second, each SW component has to be implemented for its specific target processor and requires an individual SW partitioning for each virtual design. This is timeconsuming and reduces the flexibility to explore many SW partitionings and different HW/SW mappings.

#### 2.4 High-level design exploration

High-level design exploration aims to reduce the design effort for complex systems by introducing abstract algorithm models that can be efficiently simulated and verified on virtual platforms. The Ptolemy II software environment [EJL<sup>+</sup>03,Lee10] takes a step towards event-oriented modeling of heterogeneous and embedded systems. This framework focuses on hierarchical description of complex heterogeneous systems. The main focus of Ptolemy is the hierarchical structuring and combining of multiple models into a heterogeneous system. This includes efficient ways to define nested models and sub-models and the unambiguous definition of heterogeneous systems using multiple simulation models.

In the context of high-level simulation and video coding, the area of Reconfigurable Video Coding (RVC) [CAM09, BEJ<sup>+</sup>11] has evolved recently. The prime goal of RVC is implementation independency and retargetability of video coding algorithms. It uses the CAL actor-language [EJ03] for describing the functionality of a video coding algorithm in an abstract way without taking into account any concrete implementation. Based on a CAL high-level description, an automatic transformation into an implementation language such as C or SystemC and further into a low-level representation is possible. This enables fast implementation of video coding tools in a platform-independent way.

#### 2.5 Partition Assessment Simulation in context of prior work

In a spirit similar to Ptolemy, the Partition Assessment Simulation (PAS) that is introduced in this thesis uses an event-oriented modeling approach for mimicking the execution of parallel architectures. The underlying concept behind PAS combines traditional profiling techniques and high-level modelling and simulation approaches for obtaining accurate runtime estimations of complex and virtual multi-core VCSs. While more details on the PAS will be provided in Sections 4 and 5, this section aims to set the PAS concept into the context of prior work.

The PAS can be seen as an extension of traditional dynamic runtime profiling and high-level simulation techniques. The principle of traditional dynamic profiling techniques is extended in a way that runtime complexity can be set in the context of a VCA's data structures, functional blocks and the input data that is processed. A VCA and its data-processing behaviour can be defined in an abstract way and runtime profiling information can be mapped onto these definitions. Especially for data-intensive and parallel applications such as multi-core video coding, this technique can provide essential insights into a program's runtime behaviour.

In the context of high-level simulation, the availibility of such a detailed runtime profiling information opens up new means for estimating the runtime behaviour of virtual and distributed VCAs. Multi-core HW platforms as well as VCAs can be described by high-level models. By introducing means for simulating these models and by exploiting the obtained profiling information, accurate runtime predictions become possible. Prototyping of many new virtual designs

and exploration of different parallelisation approaches can be done without needing to adapt the software design.

In contrast to CAL/RVC, PAS focuses only on modelling aspects essential to the parallel execution behaviour of a VCS and less on detailed functional description. This enables a clear focus on high-level design aspects of parallel systems without the need to specify low-level functionality (i.e. below the level where the parallelisation takes place) and results in simplicity and descriptive clarity. The PAS exploits available hardware profiling information during the high-level simulation and can make accurate runtime predictions without the need for a detailed system description.

#### 2.6 Summary

Various techniques for runtime estimation have been introduced in previous works. These techniques can be grouped into analytical, profiling-based and simulation-based methods.

Analytical estimation techniques enable performance estimations without any concrete hardware platform and only based on formal algorithm definitions. However, they are not well-suited for estimating dynamic and input-data dependent runtime behaviour of more complex video coding algorithms in an accurate way.

Statistical and instrumented profiling techniques can address this shortcoming but require a reference platform where measurements can be obtained. However, these techniques are not applicable for making runtime predictions for virtual architectures during the design phase since at this stage no implementation exists.

Simulation techniques that model the hardware architecture and runtime behaviour in a detailed (bit-accurate) way such as hardware simulation and instruction-set simulation techniques can provide accurate runtime predictions in this case. However, the modelling of a VCS using existing simulation techniques is typically too time-intensive to be usable for virtual prototyping in early design stages. The focus of these simulation approaches is on accurate modelling of the functionality and less on obtaining runtime estimates in a fast way.

The PAS methodology introduced in this thesis tries to combine existing profiling techniques and the idea of simulated runtime estimation to provide a high-level vitual prototyping solution. Efficient runtime predictions become possible in a flexible way. This is essential for fast VCS design, which has to address the short development cycles of today's video coding applications.

# CHAPTER 3

# Characteristics of modern video coding algorithms

In this chapter, the characteristics of state-of-the-art video coding algorithms and architectures are described. Understanding the fundamental structure and processes of VCAs and their impact on the hardware architecture is essential for this work. It enables us to derive the methods for performance profiling and simulation of virtual video coding systems that are introduced in later chapters. We focus on the video decoder design since parallelisation of this part of the coding process is typically more challenging than the encoder side. This results from the fact that video coding standards typically specify the decoding part (e.g. coding tools, maximum bitrate and resolution, etc.) very precisely and place strong constraints on the decoder. The encoder's functionality is rarely specified, which provides more flexibility when implementing the encoder's design. Furthermore, decoder solutions are typically located in consumer products and run on computationally less powerful hardware. This results in a high demand for computationally efficient decoder solutions.

After a short historical overview on *digital video coding* in Section 3.1, characteristics of modern video coding algorithms are introduced in Section 3.2. We use the H.264 video coding standard for characterising the structure and mechanisms of hybrid video coding. In Section 3.3, we describe how video data is typically structured in a hierarchical way for achieving resource-efficient data processing. Section 3.4 provides more details on video coding tools available in state-of-the-art video coding standards. In Section 3.5, we describe various parallelisation approaches for H.264 decoding and explain the challenges of parallel decoder designs.

# 3.1 Historical development of digital video coding

In 1984, the H.120 video coding standard [ITU93] was introduced by the ITU-T (International Telecommunication Union - Telecommunication). This coding standard was based on DPCM (Differential Pulse Code Modulation) coding and achieved video compression by reduc-

Figure 3.1: Historical development of international digital video coding standards based on the overview in [Beu10].